CoWoS究竟是甚麼?玻璃是下一波升級?產能溢出令誰有機會?-深度分析第25期:先進封裝

在AI時代,處處都是瓶頸。

我們討論過電力、記憶體,這些都是重要的瓶頸。

然而,過去一段時間,卡住 AI 喉嚨的,竟然是晶片製造流程中,過去最不起眼、利潤最薄、被視為「包裝紙」的最後一道工序:封裝 (Packaging)。

這聽起來很荒謬。就像是你買了一顆價值連城的鑽石(GPU),卻因為找不到合適的盒子(封裝),而無法把它賣給客戶。

但事實上,這已經不再是我們認知的「盒子」了。

在摩爾定律 (Moore’s Law) 瀕臨物理極限,半導體產業正在經歷一場從「微縮」到「堆疊」的典範轉移。

這場革命,讓「封裝」從配角變成了主角,從低階的勞力密集產業,變成了高階的技術軍備競賽。

這是一場關於「縫合」的藝術。誰能把更多、更強的晶片完美地縫合在一起,誰就能定義下一個十年的運算規則。

在這篇文章中,我們會一起討論以下問題:

摩爾定律的經濟學撞牆: 為什麼晶片越做越貴,逼得巨頭們不得不從「微縮」轉向「堆疊」?

CoWoS 的技術解密: 為什麼這層「矽中介層」能成為台積電壟斷 AI 訂單的最強護城河?

玻璃的革命:玻璃為何會成為下一個重點?它們何時會成真?

供應鏈的合縱連橫: 為什麼巨頭們都正在尋找「台積電以外」的備胎?外溢效果會怎樣走?

投資版圖的重劃: 在這場封裝戰爭中,除了晶圓廠,誰是賣鏟子的軍火商?誰又是地緣政治的避風港?

繼續閱讀全文,你將對半導體產業鏈有全新的認知。

第一章:矽谷的隱形天花板——當摩爾定律撞上「經濟學牆」

在過去的五十年裡,半導體行業的遊戲規則非常簡單粗暴:把東西做小。

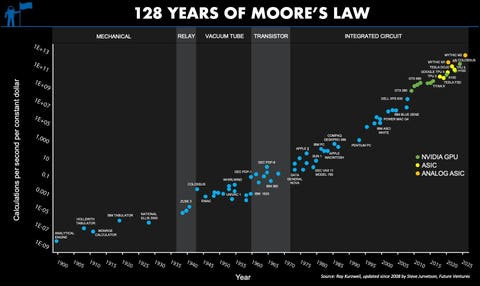

這就是著名的摩爾定律 (Moore’s Law)。每隔 18 到 24 個月,我們就能在同樣大小的矽片上,塞進兩倍數量的電晶體。

這意味著效能加倍,成本減半。這是一段被稱為「快樂微縮 (Happy Scaling)」的美好時光。

但現在,這個派對結束了。

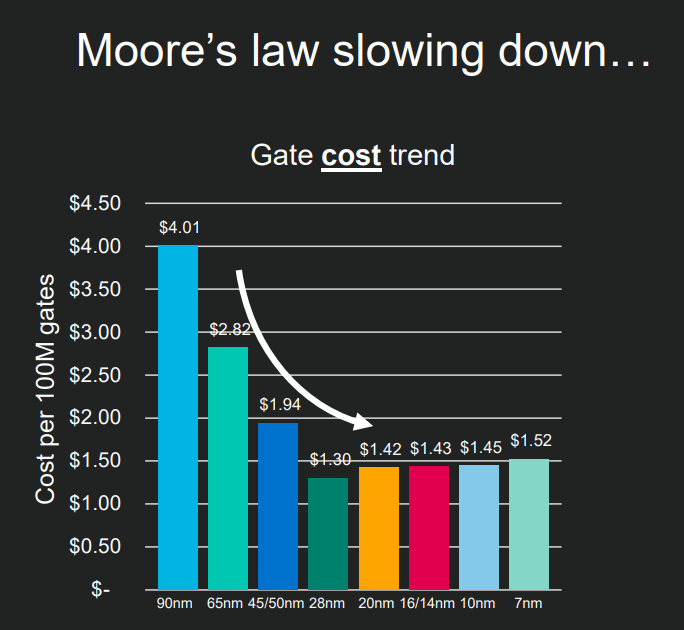

我們撞上了一堵牆。這堵牆不僅僅是物理學的(原子不能無限分割),更是經濟學的。

昂貴的微縮遊戲

隨著製程推進到 3nm、2nm,建造一座先進晶圓廠的成本已經飆升至 200 億美元以上。更糟糕的是,過去「越做越便宜」的定律失效了。現在,每單位電晶體的成本不再下降,反而開始持平甚至上升。

這導致了一個尷尬的局面:我們依然可以把晶片做小,但代價高昂到連蘋果和 Nvidia 都要猶豫三分。

但還有另一堵牆:我們也無法把晶片做「大」了。(這個稍後我們會再詳解)

我們被夾在「縮小太貴」與「變大不可能」的中間。這迫使整個產業必須改變策略,從單純的「微縮 (Scaling)」,轉向複雜的「堆疊 (Stacking)」。

事實上,在2024年,Nvidia 就選擇在他們的Blackwell 晶片使用了 4N 製程(這是 5nm 的改良版),而非使用台積電當時最頂級的 3nm。(現在Rubin晶片則開始使用3nm)

為什麼Nvidia不用 3nm?因為 5nm/4nm 技術更成熟、良率更高、成本更可控。

Nvidia 發現,與其硬上昂貴的 3nm 來提升效能,不如用稍微舊一點的製程,然後靠CoWoS 封裝把晶片拼在一起、把記憶體黏在旁邊,這樣效能更強,賺得更多。

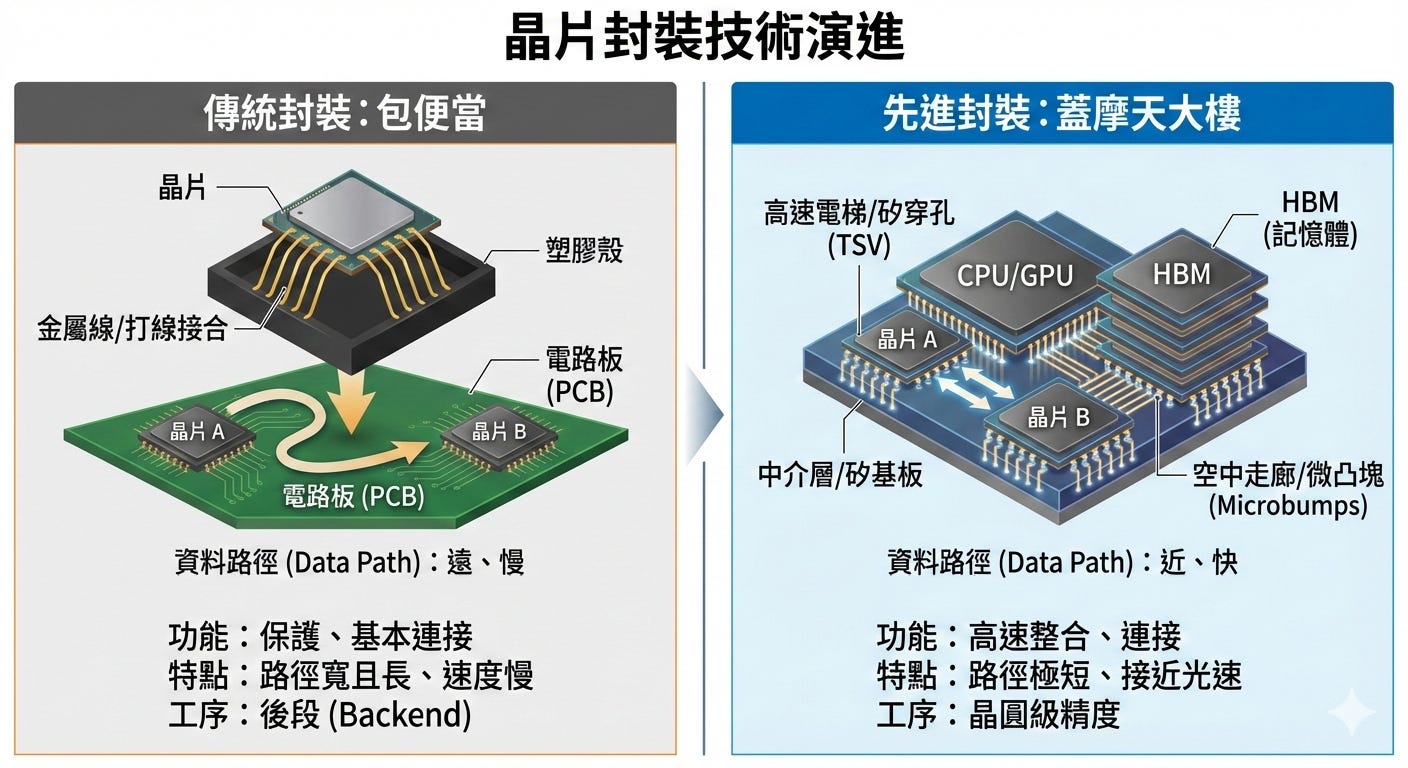

從「包便當」到「蓋摩天樓」

這就是「先進封裝」登場的時刻。

很多人以為先進封裝就是把多塊GPU 和 HBM 黏在一起,這只對了一半。

這只是「結果」,不是「技術難點」。如果只是把兩塊晶片放在同一個電路板上,那叫「拼裝」,幾十年前的技術就做得到。

先進封裝之所以難,是因為它不是把晶片「放」在一起,而是要騙過電腦,讓電腦以為它們是「同一顆晶片」。

要理解它的革命性,我們必須先打破對傳統封裝的刻板印象。

傳統封裝 :這就像是「包便當」。

晶片製造好後,非常脆弱。封裝廠(如日月光)的任務,就是用黑色的塑膠殼把它包起來,拉幾條金屬線(打線接合)連出來,讓它能插在電路板上,同時保護它不受水氣和灰塵的侵害。

晶片 A 要傳資料給晶片 B,必須先傳給底下的電路板,電路板再傳給晶片 B。這條路很寬、很慢、很遠。這是一個利潤微薄、技術含量相對較低的「後段 (Backend)」工序。先進封裝 (Advanced Packaging):這就像是「蓋摩天大樓」。

現在的晶片不是一顆單獨的處理器,而是一座由 CPU、GPU、記憶體 (HBM) 組成的「複合式建築群」。

先進封裝的任務,不再只是保護,而是「連接」。它需要在這些不同的晶片之間,搭建數以萬計的微米級「高速電梯」和「空中走廊」,讓數據能以接近光速在晶片之間穿梭。

這就像是「瞬間移動」。晶片 A 和晶片 B 靠得極近(幾乎貼在一起),中間的線路細到肉眼看不見。台積電用晶圓製造等級的精度,把不同的晶片整合在一個極小的封裝體內,實現了極高的傳輸速度。

這已經不再是「後段」工序,它實際上延續了「前段 (Frontend)」晶圓製造的技術。這也是為什麼台積電(晶圓代工廠)會跳下來做封裝的原因——因為傳統的封裝廠根本蓋不出這種摩天大樓。

摩爾定律並沒有死,它只是換了一種形式存在。它不再是關於如何在二維平面上縮小線寬,而是關於如何在三維空間中堆疊密度。

但這場革命不僅僅是技術上的,它徹底打破了半導體產業維持了三十年的權力平衡。

第一章小結:

成本反轉: 先進製程(3nm/2nm)太貴,單位電晶體成本不再下降,導致單純靠「微縮」不再划算。

策略轉向: 為了持續提升效能,產業重心從「做小晶片」轉向「堆疊晶片(先進封裝)」。

封裝升級: 封裝不再只是保護殼,而是延續摩爾定律的關鍵技術手段。

第二章:分久必合——半導體的三次版圖重劃

要理解為什麼現在「封裝」變得這麼重要,我們必須把鏡頭拉遠,看看半導體產業這 50 年來經歷了什麼樣的「分分合合」。

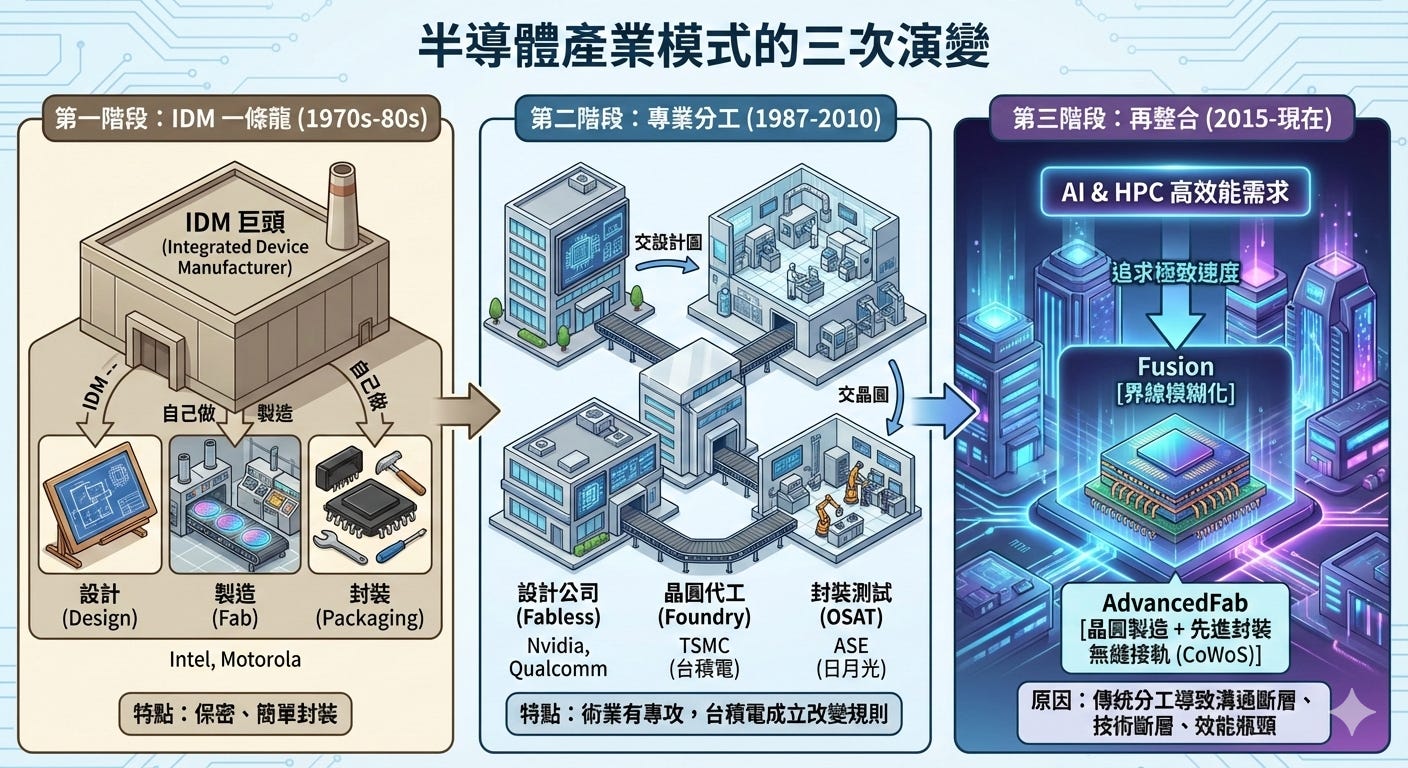

第一階段:一條龍的 IDM 時代 (1970s - 1980s)

在半導體的遠古時代,像 Intel、Motorola、TI 這些巨頭,是什麼都自己做的。這被稱為 IDM (Integrated Device Manufacturer) 模式。

設計: 自己畫圖。

製造: 自己蓋工廠(Fab)把晶片造出來。

封裝: 自己在後院把晶片包進塑膠殼裡。

那時候的封裝很簡單,就像把燈泡鎖進燈座裡一樣,技術難度低,誰做都一樣。為了保密和品質,大家習慣自己全包。

第二階段:專業分工的破碎化時代 (1987 - 2010)

1987 年,張忠謀創立台積電,開創了 Foundry (晶圓代工) 模式,徹底改變了遊戲規則。半導體產業被切成了三塊:

設計 (Fabless): 如 Nvidia、Qualcomm,只負責畫圖。

製造 (Foundry): 如台積電,只負責把圖變成矽晶圓。

封裝測試 (OSAT): 如日月光 (ASE)、Amkor,負責把晶圓切開、包裝、測試。

這個時代的邏輯是「術業有專攻」。台積電專心把晶圓造好,然後把晶圓交給日月光去封裝。這就像是台積電負責烤出頂級的披薩餅皮,然後交給必勝客去裝盒子外送。

這運作了 20 年,非常完美。直到……晶片變得太複雜了。

第三階段:被迫「再整合」的時代 (2015 - 現在)

隨著 AI 和高效能運算 (HPC) 的興起,傳統的「分工模式」出現了致命的 Bug。

溝通斷層: 當晶片線路細到奈米級時,晶圓廠(台積電)和封裝廠(日月光)之間的溝通成本變得極高。台積電造好的晶圓,送到封裝廠一加工就壞了,責任算誰的?

技術斷層: 以前的封裝只是「保護」,現在的封裝(如 CoWoS)需要用到光刻、蝕刻這些原本只屬於晶圓廠的高端技術。傳統封裝廠根本沒有這些昂貴的設備。

效能瓶頸: Nvidia 發現,如果把晶圓製造和封裝分開做,中間的訊號傳輸會有延遲。為了追求極致速度,這兩個步驟必須「無縫接軌」。

於是,歷史的鐘擺盪回來了。

台積電意識到:「如果不把封裝這塊骨頭啃下來,摩爾定律就走不下去了。」

這就是為什麼台積電要建立 3DFabric 聯盟,三星要推 3DX,Intel 要推 IDM 2.0。現在的頂級晶片,從製造到封裝,必須在同一家公司的控制下完成。

這不是為了壟斷,而是為了物理學上的必要性。這也解釋了為什麼現在封裝不再是配角,而是與製造同等重要的主角。

歷史的規律:整合與破碎的鐘擺

回顧這五十年的歷史,我們發現半導體產業遵循著一個深刻的經濟學規律:

當技術複雜度爆炸時 → 垂直整合增加:

就像現在的 CoWoS,因為晶圓設計與封裝的熱膨脹係數、電性必須完美匹配,分開做一定會失敗。所以台積電必須把封裝收回來自己做,這就是為什麼我們看到了「再整合」。

當技術標準化/商品化時 → 破碎化增加:

就像當年的電腦組裝,當介面標準統一後,誰都可以買零件來組。

我們現在正處於一個「奇點」:同時整合,又同時破碎。

這正是當下最迷人也最混亂的時刻:

整合: 在最頂尖的 AI 晶片(如 B200),製造與封裝正在緊密結合(台積電一條龍),因為這是物理極限的要求。

破碎: 但隨著新材料的出現,供應鏈又在產生新的裂痕。例如未來的「玻璃基板」和「光學引擎 (CPO)」,這些是台積電原本不擅長的領域。這給了不同的公司,成為新獨立供應商的機會。這些我們將在之後的章節詳細分析。

投資人筆記:為什麼「先進封裝」享有較高估值?

過去封裝廠(OSAT)本益比通常只有 10-15 倍,因為那是勞力密集的低毛利生意。但現在台積電做的 CoWoS 是「晶圓級封裝」,毛利率與晶圓代工相當(50%+)。

觀察重點: 不要再用傳統封裝廠的邏輯去看待先進封裝業務。市場願意給予擁有「先進封裝產能」的公司(如台積電的封裝部份、以及轉型成功的 Amkor)更高的估值倍數 (Re-rating),因為這不再是單純的加工,而是延續摩爾定律的唯一手段。

第二章小結:

鐘擺效應: 半導體產業從 IDM(一條龍)走向分工,現在為了極致效能,又回到了「再整合」。

台積電的角色: 為了物理上的連接速度,晶圓代工廠(Foundry)必須跨界吃下封裝業務。

估值邏輯改變: 先進封裝享有比傳統封裝更高的本益比,因為它具有「類晶圓製造」的高毛利特性。

第三章:物理學的惡夢——為什麼 Nvidia 必須把晶片「切開」?

在我們深入探討台積電的「封裝魔法」之前,必須先理解他們試圖打敗的怪物是什麼。

如果說 CoWoS 是台積電的「屠龍刀」,那麼它要屠的這條龍,就是一個讓所有晶片設計師都夜不成眠的物理障礙:光罩極限 (Reticle Limit)。

這也是為什麼強大如 Nvidia,在設計最新的 Blackwell B200 時,不得不做出一個打破常規的決定:把晶片切開。

完美的詛咒:當晶片大到造不出來

在過去,晶片設計的黃金法則是 SoC (System on Chip)。為了效能,工程師會盡可能把所有功能塞進「同一塊」完整的矽晶片裡。

但在 AI 時代,這種追求完美的執念撞上了一堵牆。

製造晶片的光刻機,它的曝光視窗是有物理極限的(大約是 858 mm²)。你不可能製造出一顆比這個視窗還大的單一晶片。這就像你的印表機最大只能印 A4 紙,但 Nvidia 想要印一張巨型海報。

Nvidia B200 的野心是如此巨大,單一顆晶片已經塞不下它需要的電晶體數量。

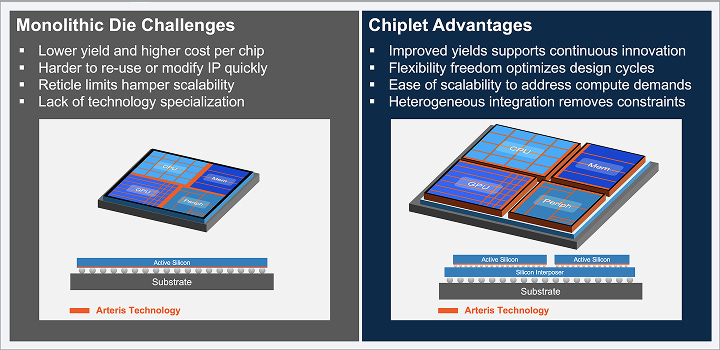

唯一的出路:Chiplet (小晶片) 策略

既然做不出一張超大披薩,Nvidia唯一的選擇,就是烤兩張達到極限大小的披薩,然後把它們「拼」在一起。

這就是 Chiplet (小晶片) 的本質。它不再追求製造單一的完美大晶片,而是將晶片「切」成不同的模組,最後再像樂高積木一樣組裝起來。

這帶來了兩個巨大的好處:

突破尺寸上限: 透過拼接,B200 的總面積實際上突破了光刻機的單次曝光極限,實現了「超規」的算力。

拯救良率與成本: 烤一張巨大的完美披薩很難(良率低),但烤兩張較小的披薩,成功率就高得多。這讓昂貴的 3nm 製程成本變得稍微可控一些。

但是,這帶來了一個致命的新問題...

把晶片切開很容易,但要把它們「黏回去」卻難如登天。

當你把一顆心臟切成兩半,再用線縫起來,血液還能流暢地流動嗎?

當訊號從第一顆晶片跑到第二顆晶片時,會遇到巨大的阻力與延遲。

如果「縫合」的技術不夠好,這顆拼湊出來的晶片,效能會遠不如單一晶片。

這就是為什麼傳統的封裝技術(用塑膠殼包起來)徹底失效了。傳統封裝的線路太粗、距離太遠,根本無法處理這種「切開再黏合」的奈米級手術。

Nvidia 需要一種技術,能把這兩顆切開的大腦,以「微米級」的精度重新接回去,讓軟體以為它們從未分開過。

誰擁有這種能進行「大腦縫合手術」的技術?

第三章小結:

光罩極限: 單一晶片面積有物理上限,Nvidia B200 等超級晶片無法一次造出來。

Chiplet 策略: 解決方案是「切開來做,再拼回去」,這能大幅提升良率並突破尺寸限制。

連接難題: 切開容易接回難,傳統封裝無法處理奈米級的拼接,這為 CoWoS 的登場鋪平了道路。

第四章:台積電的護城河——不只是造晶片,還是「造橋樑」

這就是台積電登場的時刻。

甚至在 2023 年缺貨最嚴重的時候,問題的根源並不是台積電造不出足夠的 4nm GPU 晶片,而是「封裝」產能不足。

這聽起來很荒謬。封裝(Packaging)在半導體歷史上,長期被視為技術含量低、利潤微薄的「包裝工」角色。為什麼到了 AI 時代,這個負責「包裝」的環節,竟然卡住了整個人工智慧產業的喉嚨?

答案就在台積電的獨門絕技——CoWoS (Chip-on-Wafer-on-Substrate)。

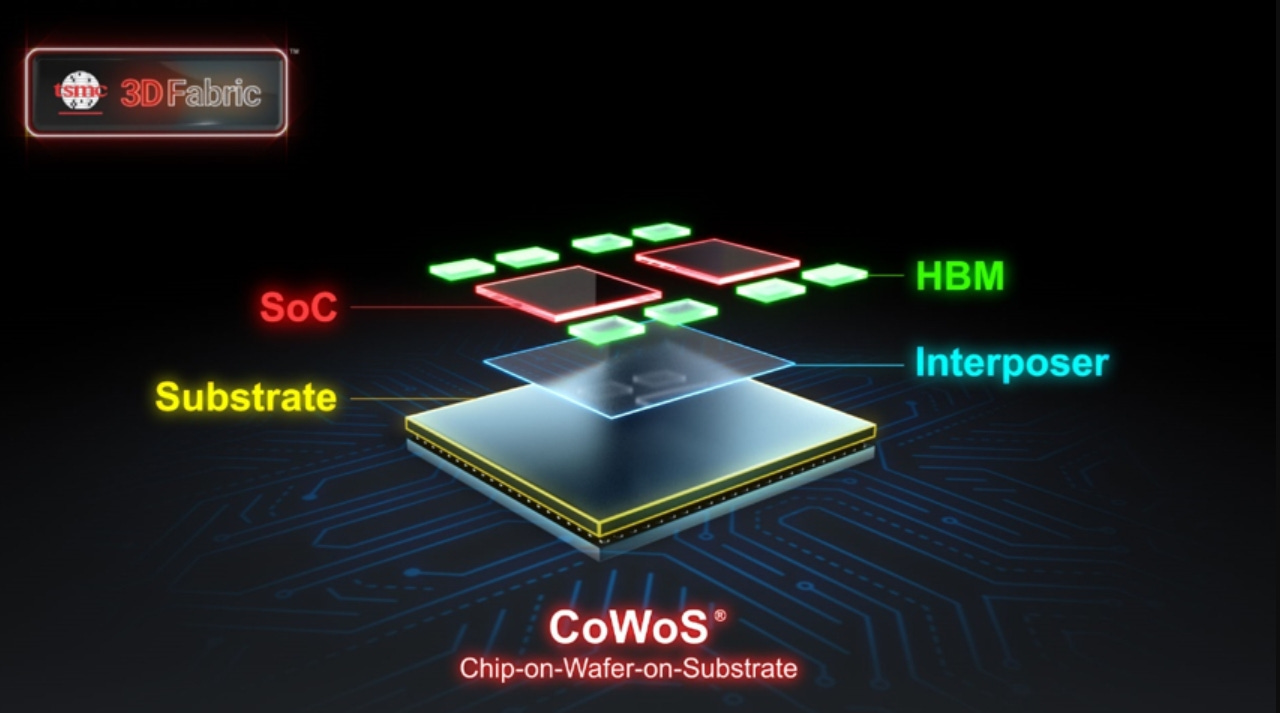

CoWoS 詳解:用「矽」來做橋樑

CoWoS 的全名揭示了它的結構:Chip-on-Wafer-on-Substrate。它的關鍵在於中間那一層,我們稱為 「矽中介層」 (Silicon Interposer)。

為了解決上一章提到的「縫合」難題,台積電提出了一個天才般的想法:「既然塑膠電路板的線路太粗,那我們為什麼不用『矽晶圓』來做連接板呢?」

要理解 CoWoS,我們先得理解 AI 晶片的結構。

一顆AI 晶片,其實不是「一顆」晶片,而是一個「晶片組合包」。它的正中央是一顆巨大的 GPU(負責運算),而緊貼著 GPU 旁邊的,是數顆 HBM(高頻寬記憶體,負責存數據)。

這兩者必須靠得非常、非常近,而且中間的連線必須非常、非常多。

想像你在蓋一棟大樓:

這棟大樓有四層結構,從下往上蓋,每一層都有它不可替代的功能:

地基:PCB 主機板 (Motherboard)

這就是你電腦機殼裡那塊綠色的大板子。它是真正的土地,線路很粗(像是公路),適合長距離傳輸電力,但沒辦法處理太精細的訊號。地下室與裙樓:ABF 載板 (Substrate)

這是 CoWoS 中的 “S”。它是一個轉接層。因為上面的晶片線路太細(像微血管),下面的土地線路太粗(像水管),直接接會漏水。所以需要這個中間層,像千層派一樣把線路慢慢散開,連到下面的大板子上。(關於這層材料的秘密,我們將在之後章節揭曉)

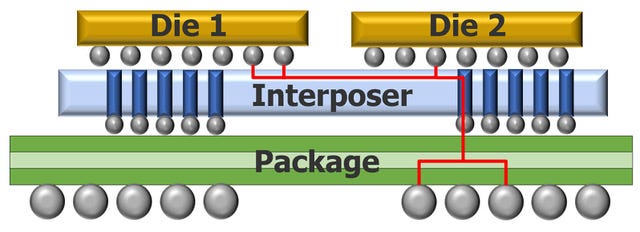

一樓大廳:矽中介層 (Silicon Interposer) —— 這就是 CoWoS 的靈魂

這是 CoWoS 中的 “oW” (on Wafer),也是台積電最核心的技術,由他們自己製造。這是一片「沒有大腦的矽晶圓」。它本身不運算,它就是一塊佈滿了奈米級超細電線的板子。

矽中介層必須使用台積電昂貴的半導體光刻機(Lithography)和蝕刻機才能製造出來,一般的封裝廠(如日月光)通常沒有這種等級的設備來製造。

這就是 Nvidia 夢寐以求的「橋樑」。 只有透過這層矽中介層,B200 的兩顆晶片才能以極高的密度互連,實現 10 TB/s 的傳輸速度,讓兩顆晶片像一顆一樣運作。然後再讓GPU 和 HBM可以互相快速傳輸資料,而且速度要像光速一樣快。

為什麼這個「中介層」這麼重要?因為 GPU 和 HBM 的線路太細、太密了(奈米級),而下面的綠色電路板線路太粗(微米/毫米級)。你不能把「奈米級的水管」直接接到「公尺級的水管」上,一定會漏水(訊號遺失)。

二樓頂級豪宅:晶片 (Chip) —— GPU 與 HBM

這是 CoWoS 中的 “C” (Chip) 。住戶 A (正中間): GPU (邏輯晶片)。這是大腦,負責運算。

住戶 B (圍在旁邊): HBM (高頻寬記憶體)。這是倉庫,負責給大腦塞資料。

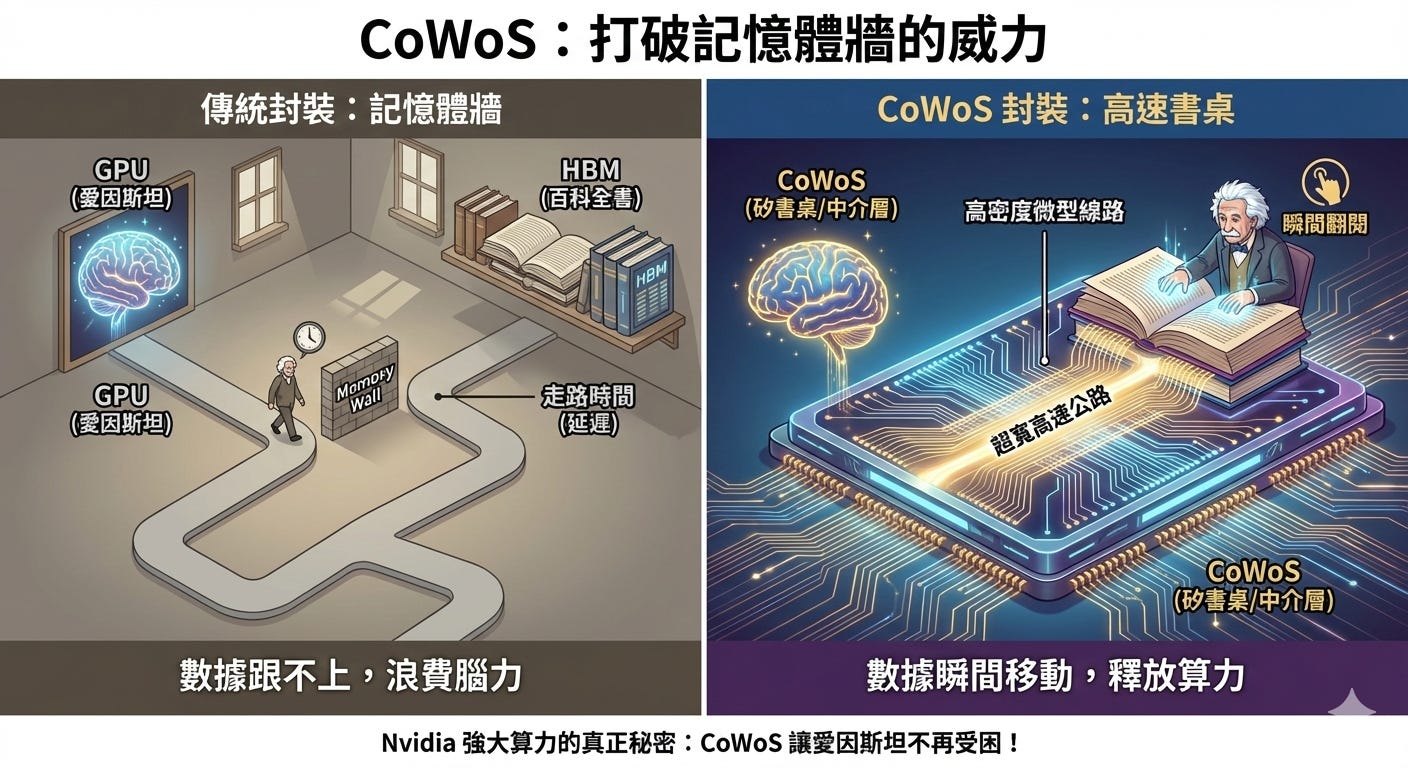

腦與書的比喻:打破記憶體牆

讓我們用一個最直觀的比喻來解釋這個技術的威力:

GPU 是「愛因斯坦」(大腦): 運算速度極快,一秒鐘能解開無數難題。

HBM 是「百科全書」(數據): 裡面寫滿了解題所需的資料。

CoWoS 是「書桌」(矽中介層):在傳統封裝裡(沒有 CoWoS):愛因斯坦坐在房間這頭,百科全書放在房間那頭的書架上。每次愛因斯坦要查資料,都得站起來走過去拿。這段「走路的時間」(延遲),浪費了愛因斯坦絕大部分的天才腦力。

這就是著名的「記憶體牆 (Memory Wall)」問題——大腦再快也沒用,因為數據跟不上。在 CoWoS 封裝裡:台積電打造了一張特殊的「矽書桌」(Interposer)。它把愛因斯坦(GPU)和百科全書(HBM)並排放在這張桌子上,兩者距離不到一毫米。更重要的是,這張桌子內部埋藏了數萬條高密度微型線路。愛因斯坦不需要起身,手一伸就能瞬間翻閱所有書籍。

這條讓數據瞬間移動的「超寬高速公路」,才是 Nvidia 晶片強大算力的真正秘密。沒有 CoWoS,GPU就只是一個困在圖書館走廊上的普通天才。

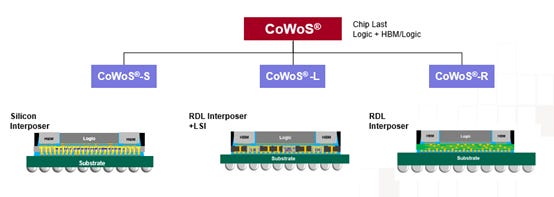

CoWoS 的進化:從「鋪地磚 (CoWoS-S)」到「蓋橋樑 (CoWoS-L)」

為了應對 B200 那種兩顆晶片拼接的需求,台積電將技術從 CoWoS-S 升級到了 CoWoS-L。

CoWoS-S: 就像整個地板都鋪昂貴的大理石(矽)。雖然平整,但太貴且容易裂。

CoWoS-L: 改用便宜的木板(有機基板)當地板,只在晶片與晶片需要溝通的關鍵連接處,嵌入一小塊大理石(LSI 矽橋)。

CoWoS-L 既保留了矽晶圓的高速傳輸特性(讓 B200 的兩顆晶片能以 10 TB/s 互通),又大幅降低了成本與破裂風險。這就是為什麼 CoWoS-L 成為了 AI 時代頂級晶片的新標準。

台積電的良率優勢

別家也能做類似的先進封裝結構(如 Intel 的 EMIB,三星的 I-Cube),但為什麼 NVIDIA 不敢輕易轉單?答案只有一個字:良率(Yield)。

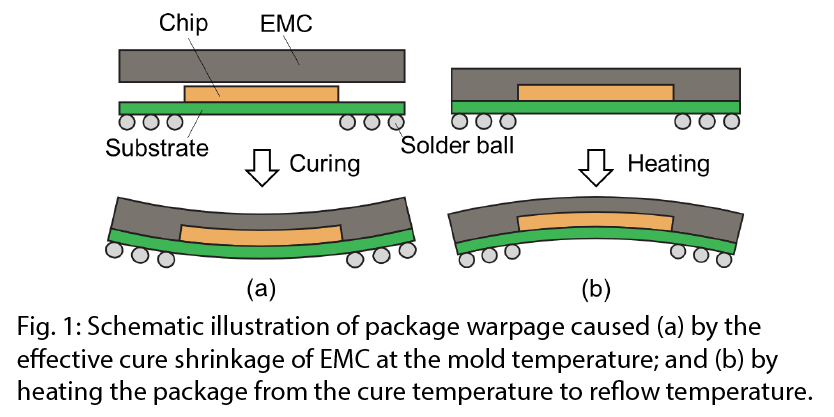

回到蓋房子的比喻。CoWoS 這棟摩天大樓的三層材料,物理性質完全不同:

上層晶片(矽): 受熱膨脹極少。

下層載板(樹脂): 受熱膨脹很大。

中介層: 夾在中間非常痛苦。

當製造過程中反覆加熱冷卻,這三層材料會像三明治一樣捲起來(翹曲,Warpage)。一旦捲起來,那些比頭髮細 100 倍的接點就會斷裂,整顆價值數萬美金的 B200 晶片直接報廢。

台積電的良率之所以獨步全球,是因為他們用四大技術支柱,硬是把這個物理難題解決了:

獨家配方克服「翹曲」

這不是買了機器就能學會的。台積電擁有獨家的膠水配方、參數與設備調整能力,能讓這塊巨大的三明治在經過幾百道工序後,依然平得像鏡子一樣。對於客戶來說,選別家就是拿幾億美金的利潤在賭博。突破光罩極限的「無縫拼接」

光刻機一次曝光的最大面積是有極限的。但 NVIDIA Blackwell 這種超級晶片加上 HBM,面積遠超極限。台積電擁有獨家黑科技,能將多次曝光的圖案「無縫接軌」。這就像別人只能烤個人小披薩,台積電卻能把麵團完美拼接,烤出巨大的家庭號披薩且中間不會斷裂。

奈米級的「打洞與焊接」精度

TSV (矽穿孔): 在中介層上打出深且直的微小孔洞並填滿銅,一旦打歪或沒填滿,訊號就會不良。

微凸塊 (Micro-bumps): 晶片底部數千個微小焊錫球,高度誤差必須控制在 ±1~2 微米。只要一顆球矮了一點點導致接觸不良,整顆晶片就完了。台積電在這兩項工藝上的良率,是競爭對手難以企及的。

CoWoS-L 與未來的混合鍵合 (Hybrid Bonding)

面對 1200W 以上的高功耗熱膨脹,台積電開發出 CoWoS-L,透過嵌入矽橋與銅導線解決變形問題。未來更將推動「銅對銅」直接連接(Hybrid Bonding),完全捨棄錫球,這就像把兩條電線直接熔接,電阻更小、速度更快。

總結來說,台積電賣的不只是封裝,而是「確定性」。在良率就是金錢的 AI 戰場上,這種確定性無可取代。

CoWoS 是大家都在用,還是只有台積電有?

這裡要釐清一個概念:CoWoS 是台積電的「商標」,就像「Big Mac」是麥當勞的一樣。雖然大家都賣漢堡(先進封裝),但只有台積電賣的能叫 CoWoS。

台積電 (TSMC): 叫 CoWoS。

英特爾 (Intel): 叫 EMIB 或 Foveros。

三星 (Samsung): 叫 I-Cube 或 X-Cube。

雖然名字不同,原理大同小異:都是想辦法把不同的晶片(GPU + HBM)塞在同一個包裝裡。

但因為 NVIDIA 的 AI 晶片幾乎全部指定用台積電,既然老大只吃 Big Mac,市場上當然都在討論 Big Mac。

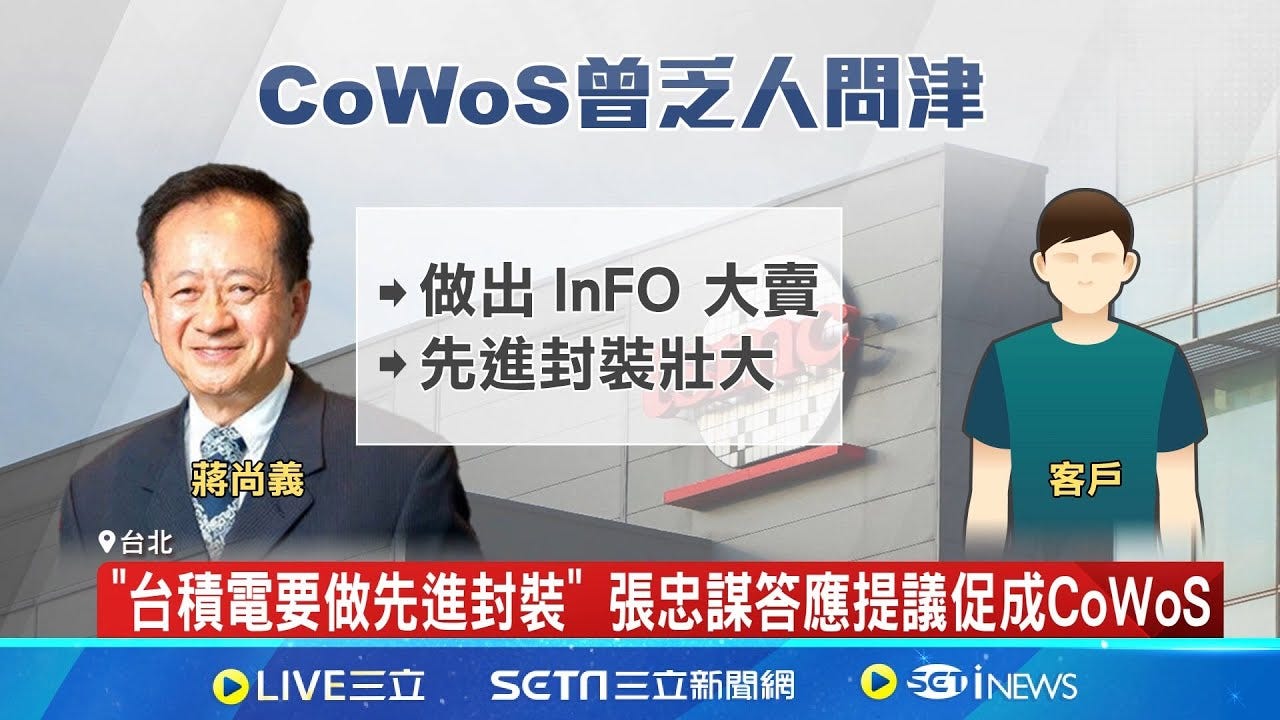

戰略地位:十年磨一劍的勝利

現在 CoWoS 是當紅炸子雞,但在 10 年前,這是一個沒人看好的賠錢貨。

這必須歸功於台積電前研發大將——蔣尚義的遠見。

早在 2011 年,蔣尚義就意識到摩爾定律即將撞牆。他提出了一個大膽的想法:台積電不應該只做晶片製造(前段),也應該跨足封裝(後段)。

當時這個決定在內部和產業界都引發了巨大的爭議:

搶客戶飯碗:封裝是日月光(ASE)、Amkor 等廠商的地盤,台積電身為代工龍頭,跨界會不會得罪合作夥伴?

技術太貴:用「矽」來做封裝基板,成本是傳統塑膠的數倍。當時除了 FPGA 廠商 Xilinx 願意嘗試,幾乎沒有客戶買單。

甚至有很長一段時間,CoWoS 產線是空置的,只有幾位工程師在維護。

但蔣尚義堅持保留這個技術團隊。他的邏輯是:「未來的高效能運算,瓶頸一定不在電晶體本身,而在於晶片之間的連接。」

十年後,AI 時代降臨。當 Nvidia 發現傳統封裝完全無法滿足 AI 模型的數據吞吐量時,他們環顧四周,驚訝地發現:全世界只有台積電一家公司,準備好了這條「矽高速公路」。

這就是為什麼在 AI 時代,台積電不只是晶片製造商,它變成了「超級整合者」。

但是,當晶圓廠拿起了手術刀,原本負責包紮的護士(封測廠),發現業務受到衝擊了。

第四章小結:

矽中介層 (Interposer): CoWoS 的核心是用「矽」做橋樑,讓 GPU 與 HBM 實現極短距離、極高速度的互連。

記憶體牆: CoWoS 解決了運算(GPU)與數據(HBM)之間的傳輸瓶頸。

良率壁壘: 台積電獨步全球的關鍵,在於解決了異質材料堆疊時的「翹曲」與「對準」問題,提供了確定性。

第五章:地盤的重劃——當晶圓廠搶了封測廠的飯碗

在先進封裝的戰場上,半導體產業的傳統分工界線正在消失。

過去,晶片製造(前段)與封裝測試(後段)是兩個截然不同的世界。晶圓廠(如台積電)負責把電路刻在矽片上,技術極難、利潤極高;封測廠(如日月光、Amkor)負責把晶片包進塑膠殼裡,技術相對簡單、利潤微薄。

但 CoWoS 的出現,打破了這個默契。

降維打擊:為什麼台積電必須跨界

CoWoS 的核心——矽中介層 (Silicon Interposer),本質上就是一片「矽晶圓」。要在上面蝕刻比頭髮還細 100 倍的線路,需要的是昂貴的光刻機與蝕刻機。

這正是台積電的強項,卻是傳統封測廠的軟肋。日月光家裡只有處理塑膠和金屬的設備,沒有這種處理奈米級矽晶圓的重裝備。

於是,台積電順理成章地跨過了那條線。它告訴客戶:「這顆晶片是我造的,我最懂它的脾氣。交給我封裝,風險最低。」這種「製造 + 封裝」的一條龍服務,讓台積電獨吞了 AI 產業利潤最豐厚的「頂層肉」。

這就是為什麼在 AI 時代,台積電不再只是晶片製造商,它變成了「超級整合者」。

傳統諸侯的焦慮:OSAT 的生存戰

他們發現,原本屬於他們的「封裝」業務,只要是利潤最高、技術最難的那一塊(如 AI 伺服器),都被台積電搶走了。

現在,台積電與封測廠之間更像是一種「富人吃肉,管家喝湯」的共生關係。

為了專注於利潤最高的矽中介層製造(CoWoS 的核心),台積電其實會將最後一段利潤較低的「組裝到載板(CoWoS-OS)」工序,外包給日月光或 Amkor。

這意味著,只要台積電的肉吃得越多,日月光分到的湯也就越多,兩者並非純粹的競爭,而是上下游的盟友。

傳統的封測龍頭(OSAT)很清楚,不是所有的晶片都像 Nvidia B200 那麼昂貴,也不是所有產品都用得起 CoWoS。

他們瞄準了「先進封裝 Lite」市場。

Fan-out (扇出型封裝): 這是 OSAT 的主戰場。例如蘋果 iPhone 的處理器,使用的技術邏輯就與此相近。

SiP (系統級封裝): 這是日月光的強項。將藍牙、Wi-Fi、處理器全部塞進一個小黑盒子裡,這在穿戴式裝置(如 Apple Watch)中至關重要。

OSAT 的生存之道: 他們賭的是「量」。AI 晶片雖然貴,但數量有限;而手機、汽車、物聯網裝置的數量是海量的。他們正在將先進封裝技術「下放」,吃下這個龐大的中高階市場。

然而,隨著技術演進,這場戰爭即將迎來一個新的變數,一個可能顛覆現有棋盤的新材料——玻璃。

第五章小結:

降維打擊: 台積電利用晶圓級設備做封裝,搶走了利潤最豐厚的頂層市場。

共生關係: 台積電專注於核心的中介層製造,將後段組裝外包給 OSAT(如日月光),形成「吃肉喝湯」的聯盟。

OSAT 的出路: 傳統封測廠轉向 Fan-out 與 SiP 技術,主攻量大面廣的手機與車用市場。

第六章:玻璃基板 (Glass Substrate)——下一場材料革命

我們剛剛花了很多篇幅講述矽中介層 (Silicon Interposer) ,但是大家還記得一塊AI晶片是由什麼組成的嗎?

對了,我們還未討論那個默默無聞但至關重要的配角:基板 (Substrate)。

矽中介層是讓GPU和HBM互相溝通的橋樑,而基板則是晶片與電路板之間的橋樑。

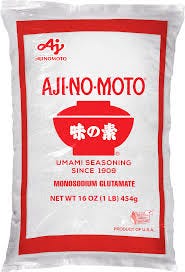

CoWoS 中的 “S”:味精公司壟斷的秘密

CoWoS 的最後一個字 S (Substrate),指的就是最底下那塊板子。目前主流使用的是 ABF 載板。

這是一個非常有趣的日本壟斷故事。這種板子的核心絕緣材料叫 ABF (Ajinomoto Build-up Film)。

你沒看錯,它的發明者正是那家做味精的日本公司——味之素 (Ajinomoto)!

這是一個關於「廢物利用」變成「黑科技」的傳奇故事。

Keep reading with a 7-day free trial

Subscribe to FOMO研究院電子報 to keep reading this post and get 7 days of free access to the full post archives.